# Lecture 21: Virtual Memory II

- · Last Lecture:

- Introduction to virtual memory

- Today

- Review and continue virtual memory discussion

- Next time

- Guest lecture, Ron Kalla, IBM

UTCS CS352, S05 Lecture 21

1

# Goals of virtual memory

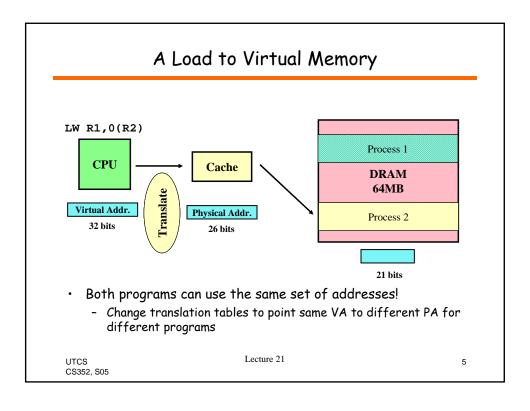

- Make it appear as if each process has:

- Its own private memory

- Nearly infinite-sized memory

UTCS CS352, S05 Lecture 21

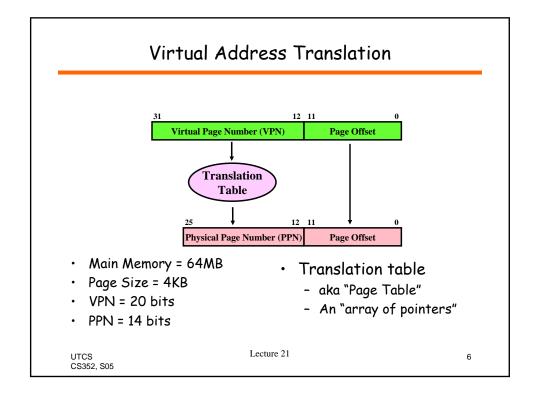

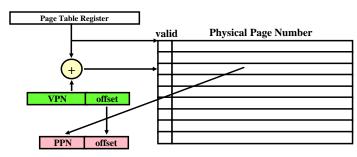

# Page Table Construction

- · Page table size

- (14 + 1) \* 2<sup>20</sup> = 4MB

- · Where to put the page table?

UTCS CS352, S05 Lecture 21

7

## What else can we put in this table?

- · What if we want a page to be read-only?

- · What if we want a page to only hold instructions?

- · What if we want to keep track of "dirty" pages?

UTCS CS352, S05 Lecture 21

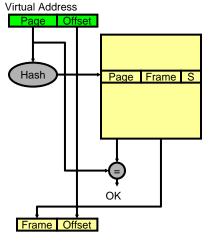

## Inverted Page Tables

- Only store table entries for pages in physical memory

- Miss in page table implies page is on disk

- Usual hash-table rules apply:

- Hash table should not be full

- Rule of thumb: at least twice as many hash table entries as there are pages in memory.

UTCS Lecture 21 11 CS352, S05

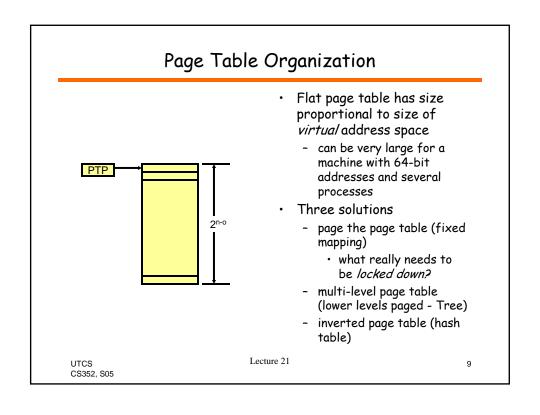

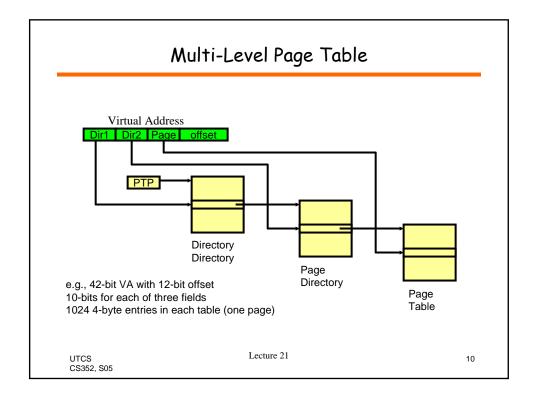

#### Summary so far

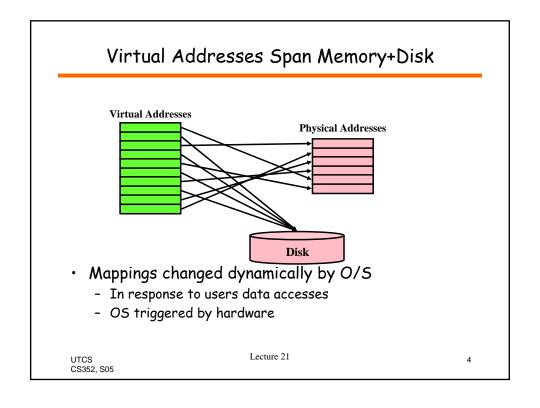

- Virtual memory provides

- Illusion of private memory system for each process

- Protection

- Relocation in memory system

- Demand paging

- But page tables can be large

- Motivates: paging page tables, multi-level tables, inverted page tables

- Next:

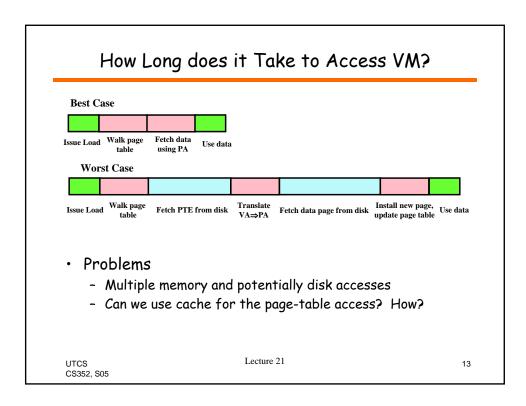

- How can we improve performance of page tables?

UTCS Lecture 21 12 CS352, S05

#### "Rare" Behavior in VM system

- TLB Miss

- Translation is not in TLB but everything could be in memory

- Two approaches

- · Hardware state machine walks the page table

- fast but inflexible

- · Exception raised and software walks the page table

- Page Fault

- Entry not in TLB and target page not in main memory

- Worst case

- Page fault and page table and target page

UTCS CS352, S05 Lecture 21

15

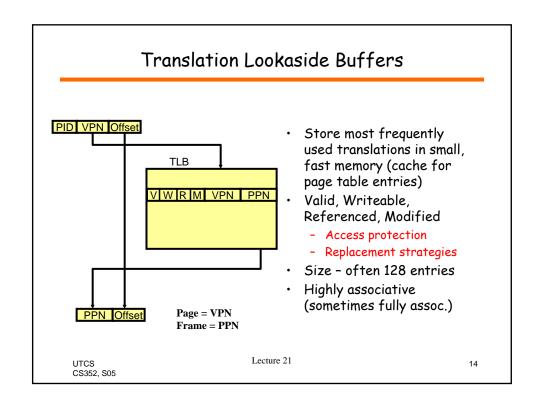

#### Reducing TLB misses

- Same type of optimizations as for cache

- Associativity (many TLBs are fully associative)

- Capacity TLBs tend to be 32-128 entries

- · Adjust page size

- Small pages

- Reduces internal fragmentation

- · Speeds page movement to/from disk

- Large pages

- Can cover more physical memory with same number of TLB entries

- Solution typically have a variable page size

- Select by OS, 4KB-256KB (superpages)

UTCS CS352, S05 Lecture 21

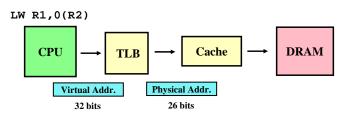

## Virtual Memory + Caching

- · Conflicting demands:

- Convenience of flexible memory management (translation)

- Performance of memory hierarchy (caching)

- Requires cooperation of O/S

- Data in cache implies that data is in main memory

- Combine VM and Caching

- Where do we put the Cache and the TLB????

UTCS CS352, S05 Lecture 21

17

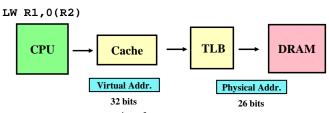

### Physically Addressed Cache

- Translate first from VA ⇒ PA

- · Access cache with PA

- Problems?

UTCS CS352, S05 Lecture 21

## Virtually Addressed Cache

- · Access cache first

- Only translate if going to main memory

- Problems?

UTCS CS352, S05 Lecture 21

19

#### Virtually addressed caches give aliasing problems

- Can occur when switching among multiple address spaces

- Synonym aliasing

- Different VAs point to the same PA

- Occurs when data shared among multiple address spaces

- One solution always translate before going to the cache

- Homonym aliasing

- Same VA point to different PAs

- Occurs on context switching

- Two solutions:

- · Flush TLB on process switch/system call

- · TLB includes process ID

UTCS CS352, S05 Lecture 21

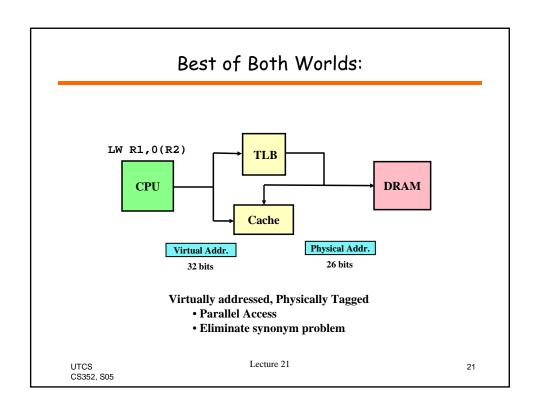

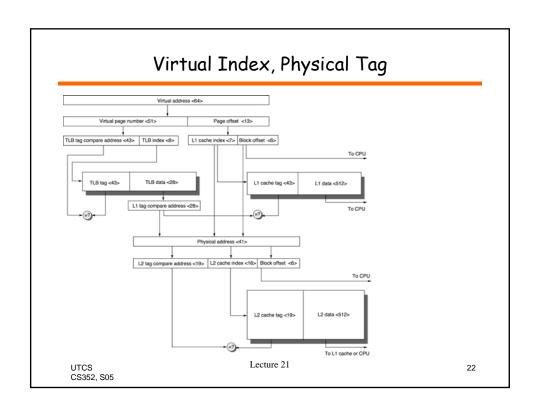

#### Other Aliasing Solutions

- Note virtually indexed/physically tagged put constraints on cache capacity, page size, etc.

- Other solutions:

- 21264: 8KB pages, 64KB i-cache, 2-way set associative

- · Aliases could reside in 8 different places in cache

- · On cache miss, invalidate any possible aliases in cache

- Intel Pentium 4

- · Virtually indexed/virtually tagged cache

- Check for TLB misses off line (roll back if necessary)

UTCS CS352, S05 Lecture 21

23

#### Virtual Memory Summary

- Relocation, Protection

- Apparent memory size >> DRAM capacity

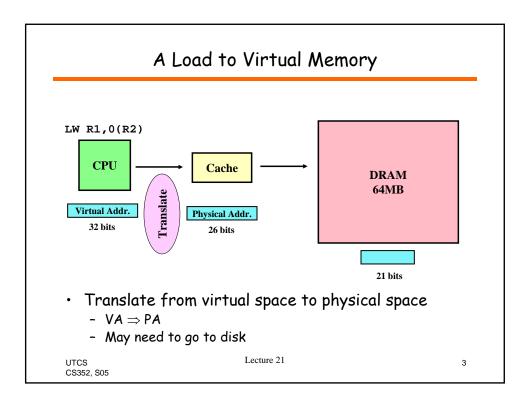

- Translation

- From large VA space to smaller PA space

- Page tables hold translations

- Provides

- Separation of memory management from user programs

- Ability to use DRAM as cache for disk

- Fast translation using Translation Lookaside Buffer (TLB)

- · Cache for page table

- Speed translate in parallel with cache lookup

UTCS CS352 S05 Lecture 21