## Lecture 10: Datapath Control; Multicycle

- Organizational

- We're still grading the exams; hopefully done on Thursday

- Hand out HW #3, due a week from today

- Partial solutions to HW #3 available on Thursday

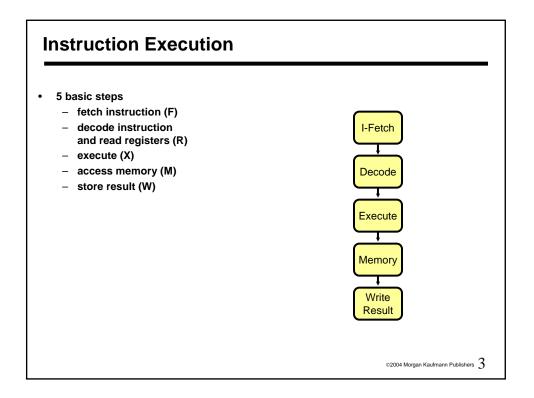

- Last Time

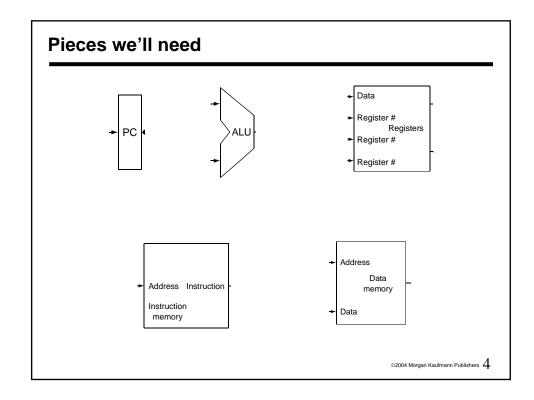

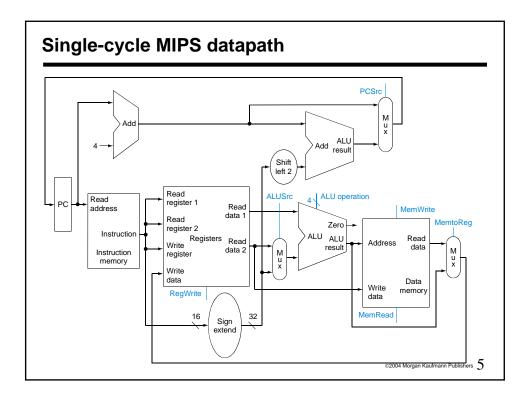

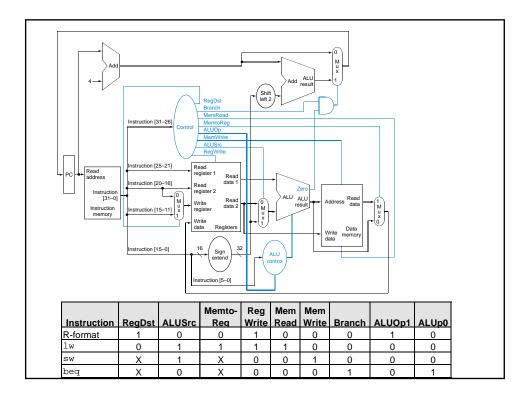

- Datapath organization

- Today

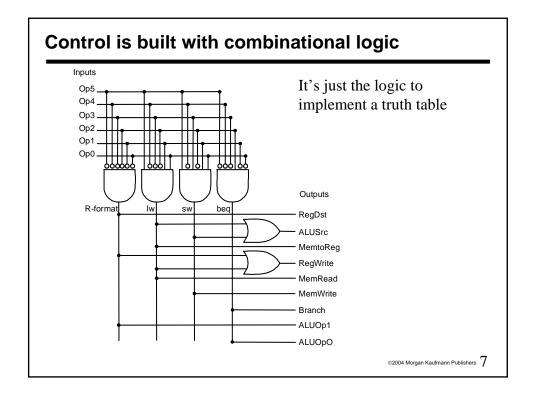

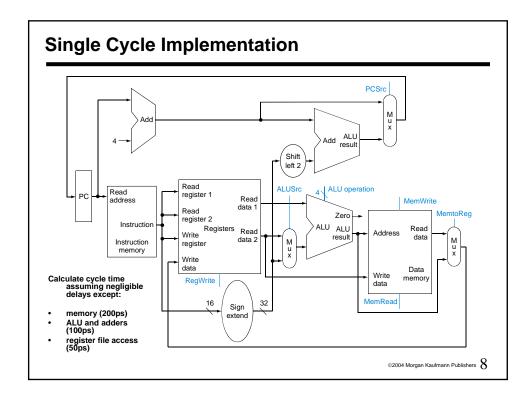

- Datapath Control

- Multicycle Machine

- Introduction to Pipelining (if we have time)

©2004 Morgan Kaufmann Publishers

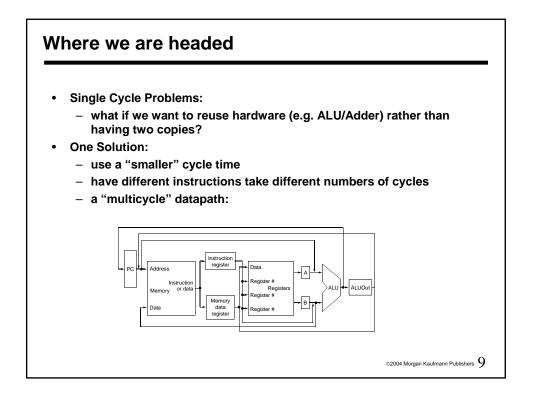

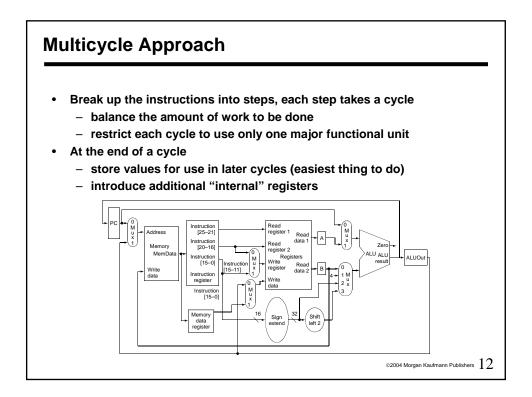

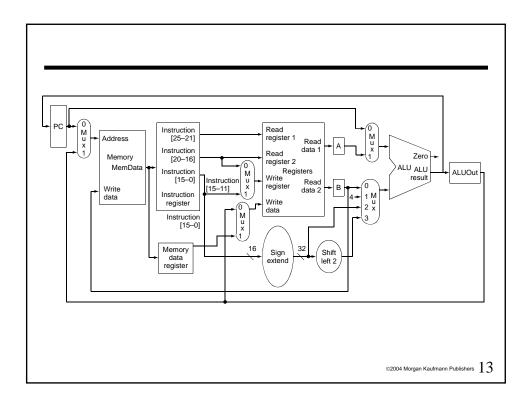

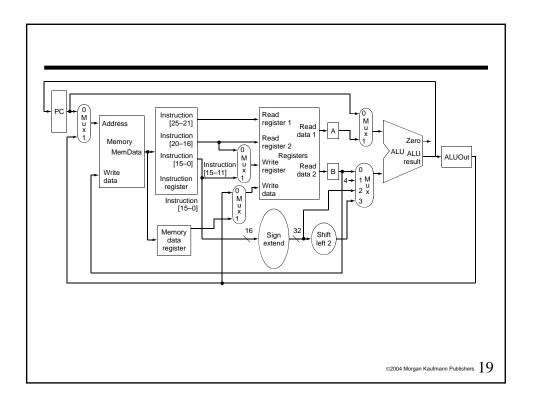

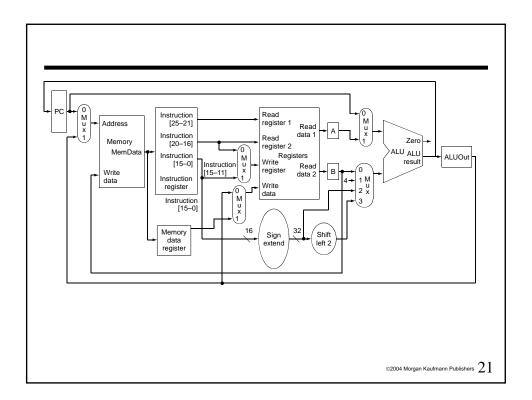

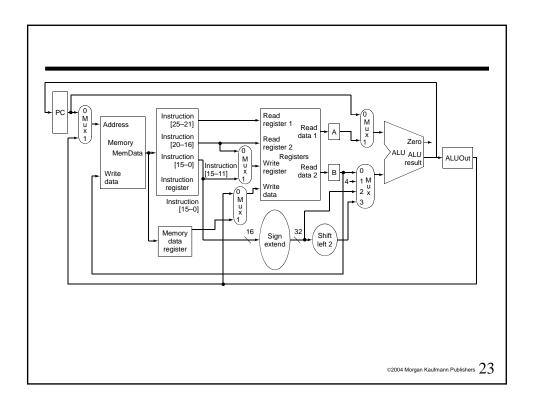

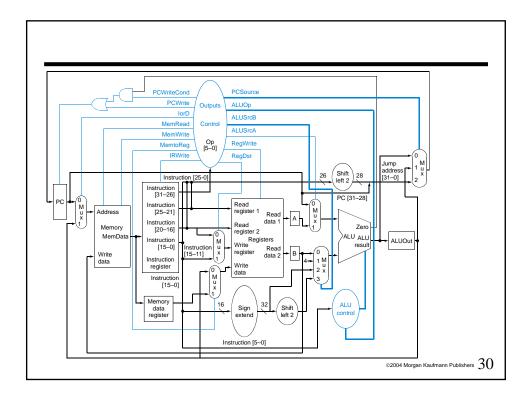

## **Multicycle Approach**

٠

- We will be reusing functional units

- ALU used to compute address and to increment PC

- Memory used for instruction and data

- Our control signals will not be determined directly by instruction

- e.g., what should the ALU do for a "subtract" instruction?

- We'll use a finite state machine for control

©2004 Morgan Kaufmann Publishers 11

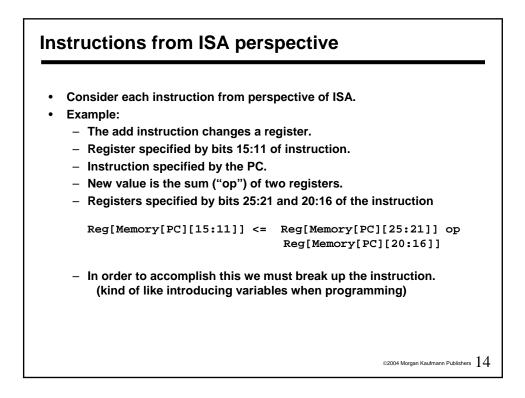

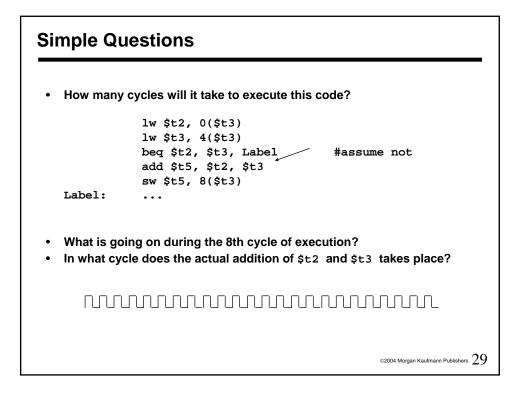

## Breaking down an instruction

• ISA definition of arithmetic:

Reg[Memory[PC][15:11]] <= Reg[Memory[PC][25:21]] op Reg[Memory[PC][20:16]]

- Could break down to: - IR <= Memory[PC]

- A <= Reg[IR[25:21]]

- B <= Reg[IR[20:16]]

- ALUOut <= A op B

- Reg[IR[20:16]] <= ALUOut

- We forgot an important part of the definition of arithmetic!

PC <= PC + 4</li>

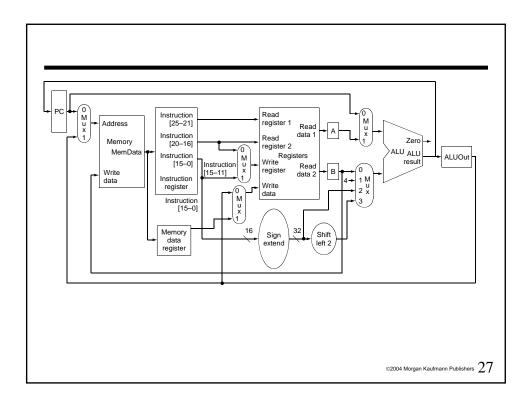

| Step name                                                                                                                                                          | Action for R-type<br>instructions                                                                                       | Action for memory-<br>reference instructions                                                                                                                                                                                                                                           | Action for<br>branches                                                                           | Action for<br>jumps                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

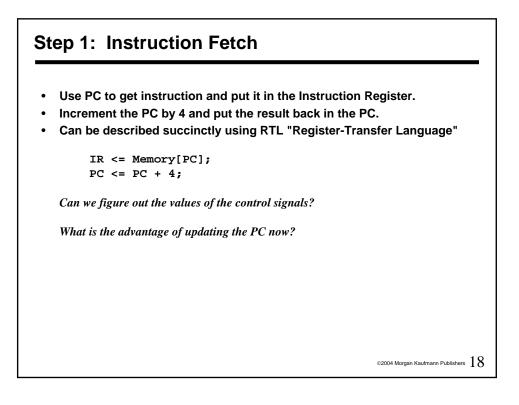

| Instruction fetch                                                                                                                                                  | IR <= Memory[PC]<br>PC <= PC + 4                                                                                        |                                                                                                                                                                                                                                                                                        |                                                                                                  |                                                                                  |

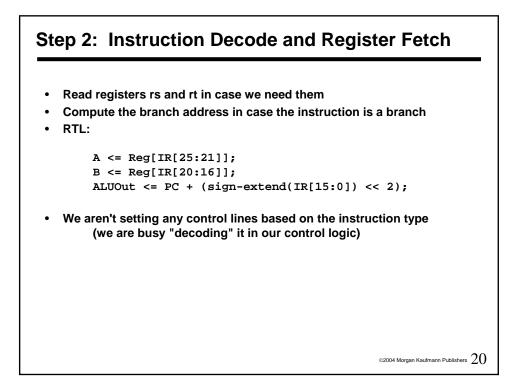

| Instruction decode/register fetch                                                                                                                                  | $A \le Reg [IR[25:21]]$<br>$B \le Reg [IR[20:16]]$<br>ALUOtt = PC + (sign-starton (R[25:0]) << 2)                       |                                                                                                                                                                                                                                                                                        |                                                                                                  |                                                                                  |

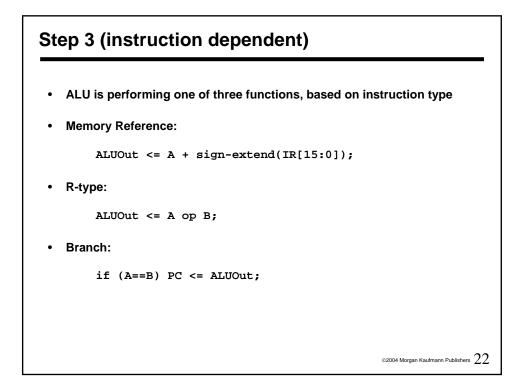

| Execution, address computation,<br>branch/jump completion                                                                                                          | ALUOUt <= A op B                                                                                                        | ALUOut <= A + sign-extend<br>(IR[15:0])                                                                                                                                                                                                                                                | If (A == B)<br>PC <= ALUOUt                                                                      | PC <= {PC [31:28],<br>(IR[25:0]],2'b00)}                                         |

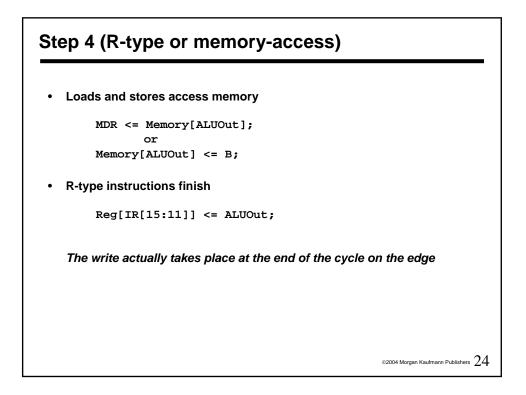

| Memory access or R-type<br>completion                                                                                                                              | Reg [IR[15:11]] <=<br>ALUOut                                                                                            | Load: MDR <= Memory[ALUOut]<br>or<br>Store: Memory [ALUOut] <= B                                                                                                                                                                                                                       |                                                                                                  |                                                                                  |

| Memory read completion                                                                                                                                             |                                                                                                                         | Load: Reg[IR[20:16]] <= MDR                                                                                                                                                                                                                                                            |                                                                                                  |                                                                                  |

| the instruction class. The empty em<br>takes fewer cycles. In a multicycle in<br>not idle or wasted. As mentioned ea<br>ister file are identical. In particular, i | ries for the Memory acces<br>nplementation, a new ins<br>rlier, the register file actua<br>the value read into register | here steps, an instruction takes from one to<br>is step or the Memory read completion ste<br>truction will be started as scon as the cur<br>Illy reads every cycle, but as long as the IR.<br>B during the Instruction decode stage, for<br>sed in the Memory access stage for a store | p indicate that the pa<br>rent instruction comp<br>does not change, the<br>a branch or R-type in | rticular instruction cla<br>pletes, so these cycles a<br>values read from the re |

## <section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><text><list-item><list-item><list-item><list-item><list-item><list-item>