| <ul> <li>Two-person programming teams</li> <li>Work side-by-side <ul> <li>One person "drives" (types the code)</li> <li>Other person watches, thinks, and makes suggestior</li> <li>Two brains are better than one</li> </ul> </li> <li>One grade per team</li> <li>Pick your own partner</li> </ul> | S  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <ul> <li>One person "drives" (types the code)</li> <li>Other person watches, thinks, and makes suggestion</li> <li>Two brains are better than one</li> <li>One grade per team</li> </ul>                                                                                                             | S  |

| <ul> <li>Other person watches, thinks, and makes suggestion</li> <li>Two brains are better than one</li> <li>One grade per team</li> </ul>                                                                                                                                                           | S  |

| 5                                                                                                                                                                                                                                                                                                    |    |

| · Pick your own partner                                                                                                                                                                                                                                                                              |    |

| <ul> <li>Find someone with similar skill level as you</li> </ul>                                                                                                                                                                                                                                     |    |

| <ul> <li>And a compatible schedule</li> <li>OK to change after this assignment</li> </ul>                                                                                                                                                                                                            |    |

| <ul> <li>Issues to be aware of:</li> </ul>                                                                                                                                                                                                                                                           |    |

| <ul> <li>Both partners must learn; take turns driving</li> <li>It takes time to get used to this programming meth</li> </ul>                                                                                                                                                                         | bd |

| <ul> <li>Implicit control on each<br/>instruction</li> </ul>                                                                                                                                                                                                                                                                                                      |       |                                  |                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------|-----------------------------------------------------------------------------|

| $PC \leftarrow PC + 4$ • Unconditional jumps<br>$PC \leftarrow X \text{ (direct)}$ $PC \leftarrow PC + X (PC \text{ relative)}$ $X \text{ can be constant or}$ $\text{register}$ • Conditional jumps (branches)<br>$PC \leftarrow PC + ((\text{cond})?X:4)$ • Predicated instructions<br>• Conditions<br>- flags<br>- in a register<br>- fused compare and branch | LOOP: | LOAD<br>ADD<br>ADD<br>CMP<br>JNE | R1 <- (R5+R2)<br>R3 <- R3 + R1<br>R2 <- R2 + 4<br>R4 <- R2 == 8<br>R4, LOOP |

| Constant Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|

| <ul> <li>Integer constants <ul> <li>mostly small</li> <li>positive or negative</li> </ul> </li> <li>Bit fields <ul> <li>contiguous field of 1s<br/>within 32bits (64 bits)</li> </ul> </li> <li>Other <ul> <li>addresses, characters,<br/>symbols</li> </ul> </li> <li>A good architecture <ul> <li>uses a few bits to encode<br/>the most common.</li> <li>allows any constant to be<br/>generated (table<br/>reference)</li> </ul> </li> </ul> | 6 VAX short literal<br>Op -32 to 31<br>5 5<br>E S Symbolics 3600<br>Bit Fields |  |

| UTCS<br>CS352, S05                                                                                                                                                                                                                                                                                                                                                                                                                               | ecture 5 20                                                                    |  |

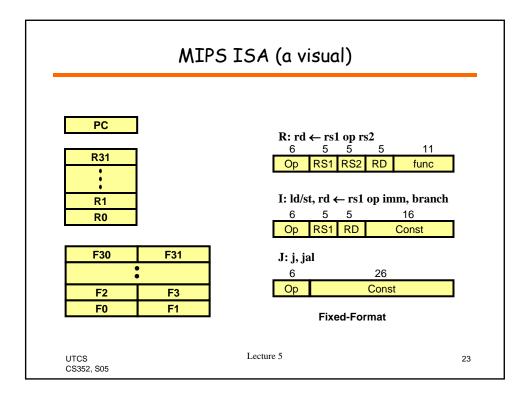

|                                                                                                                                                                                                                                                                                                      | MIPS ISA                                                                                                                                                                                             |                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

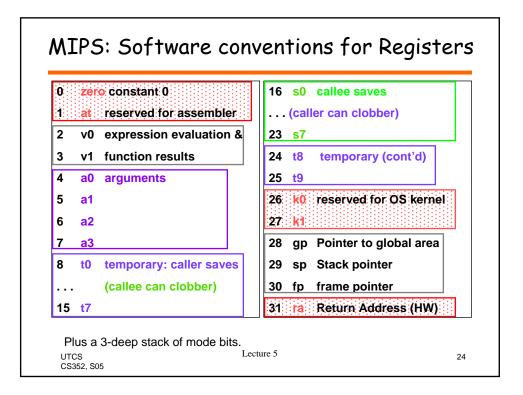

| <ul> <li>R0=0, other re</li> <li>32 FP registers <ul> <li>16 double-pre</li> <li>8, 16, and 32 bit</li> <li>Load/Store arcl</li> <li>Simple addressi <ul> <li>Immediate</li> <li>Displacement</li> </ul> </li> <li>Simple fixed ins</li> <li>Fused compare of sequences (ie. re</li> </ul></li></ul> | ision (use adjacent 32-bit registing<br>integer data types<br>nitecture (no memory operation<br>modes<br>R1 $\leftarrow$ 0x23<br>R2 $\leftarrow$ d(Rx) 0(R3), 0x100<br>truction format (3 types), 90 | s (SP, FP, RA, etc.)<br>ters)<br>ons in ALU ops)<br>00(RO)<br>instructions<br>sized into simple<br>of shift and mask) |

| UTCS<br>CS352, S05                                                                                                                                                                                                                                                                                   | Lecture 5                                                                                                                                                                                            | 22                                                                                                                    |

| Instruction       | Example           | Meaning                                 | <u>Comments</u>                       |

|-------------------|-------------------|-----------------------------------------|---------------------------------------|

| add               | add \$1,\$2,\$3   | 1 = 2 + 3                               | 3 operands; exception possible        |

| subtract          | sub \$1,\$2,\$3   | 1 = 2 - 3                               | 3 operands; exception possible        |

| add immediate     | addi \$1,\$2,100  | 1 = 2 + 100                             | + constant; <u>exception possible</u> |

| add unsigned      | addu \$1,\$2,\$3  | 1 = 2 + 3                               | 3 operands; <u>no exceptions</u>      |

| subtract unsigned | subu \$1,\$2,\$3  | 1 = 2 - 3                               | 3 operands; <u>no exceptions</u>      |

| add imm. unsign.  | addiu \$1,\$2,100 | 1 = 2 + 100                             | + constant; <u>no exceptions</u>      |

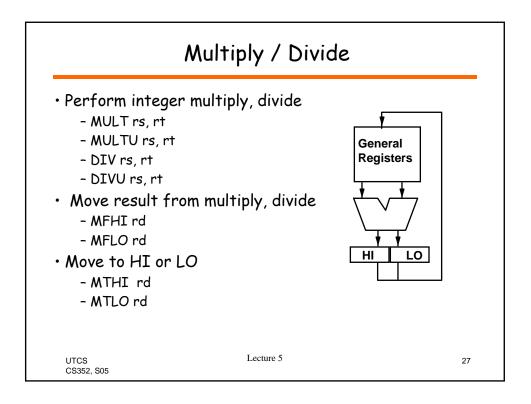

| multiply          | mult \$2,\$3      | Hi, Lo = \$2 x \$3                      | 64-bit signed product                 |

| multiply unsigned | multu\$2,\$3      | Hi, Lo = \$2 x \$3                      | 64-bit unsigned product               |

| divide            | div \$2,\$3       | $Lo = $2 \div $3,$<br>$Hi = $2 \mod $3$ | Lo = quotient, Hi = remainder         |

| divide unsigned   | divu \$2,\$3      | $Lo = $2 \div $3,$                      | Unsigned quotient & remainder         |

|                   |                   | Hi = \$2 mod \$3                        |                                       |

| Move from Hi      | mfhi \$1          | 1 = Hi                                  | Used to get copy of Hi                |

| Move from Lo      | mflo \$1          | \$1 = Lo                                | Used to get copy of Lo                |

|                     |                   |                            |                                | _ |

|---------------------|-------------------|----------------------------|--------------------------------|---|

| Instruction         | Example           | Meaning                    | Comment                        |   |

| and                 | and \$1,\$2,\$3   | \$1 = \$2 <b>&amp;</b> \$3 | 3 reg. operands; Logical AND   |   |

| or                  | or \$1,\$2,\$3    | \$1 = \$2   \$3            | 3 reg. operands; Logical OR    |   |

| xor                 | xor \$1,\$2,\$3   | \$1 = \$2 Å \$3            | 3 reg. operands; Logical XOR   |   |

| nor                 | nor \$1,\$2,\$3   | 1 = (2   3)                | 3 reg. operands; Logical NOR   |   |

| and immediate       | andi \$1,\$2,10   | 1 = 2 & 10                 | Logical AND reg, constant      |   |

| or immediate        | ori \$1,\$2,10    | 1 = 2   10                 | Logical OR reg, constant       |   |

| xor immediate       | xori \$1, \$2,10  | \$1 = ~\$2 &~10            | Logical XOR reg, constant      |   |

| shift left logical  | sll \$1,\$2,10    | 1 = 2 << 10                | Shift left by constant         |   |

| shift right logical | srl \$1,\$2,10    | 1 = 2 >> 10                | Shift right by constant        |   |

| shift right arithm. | sra \$1,\$2,10    | 1 = 2 >> 10                | Shift right (sign extend)      |   |

| shift left logical  | sllv \$1,\$2,\$3  | 1 = 2 << 3                 | Shift left by variable         |   |

| shift right logical | srlv \$1,\$2, \$3 | 1 = 2 >> 3                 | Shift right by variable        |   |

| shift right arithm. | srav \$1,\$2, \$3 | 1 = 2 >> 3                 | Shift right arith. by variable |   |

| 8                   |                   |                            |                                |   |

| Instruction        | Comment                                           |

|--------------------|---------------------------------------------------|

| SW 500(R4), R3     | Store word                                        |

| SH 502(R2), R3     | Store half                                        |

| SB 41(R3), R2      | Store byte                                        |

| LW R1, 30(R2)      | Load word                                         |

| LH R1, 40(R3)      | Load halfword                                     |

| LHU R1, 40(R3)     | Load halfword unsigned                            |

| LB R1, 40(R3)      | Load byte                                         |

| LBU R1, 40(R3)     | Load byte unsigned                                |

| LUI R1, 40         | Load Upper Immediate (16 bits shifted left by 16) |

| Why need LU        | LUI R5                                            |

| , -                |                                                   |

| UTCS<br>CS352, S05 | R5 0000 0000                                      |

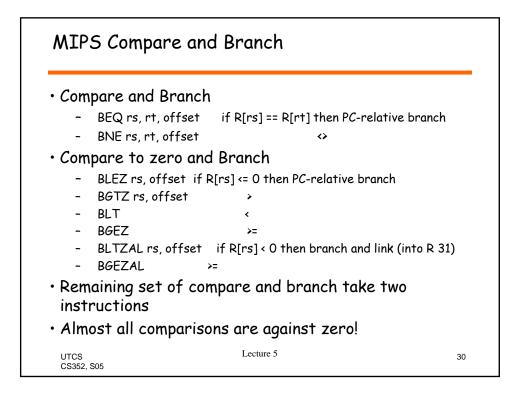

| <b>Instruction</b>  | Example                               | Meaning                                                  |

|---------------------|---------------------------------------|----------------------------------------------------------|

| branch on equal     | beq \$1,\$2,100<br>Equal test; PC rel | if $(\$1 == \$2)$ go to PC+4+100<br>lative branch        |

| branch on not eq.   | bne \$1,\$2,100<br>Not equal test; PC | if (\$1!= \$2) go to PC+4+100<br><i>C relative</i>       |

| set on less than    | slt \$1,\$2,\$3<br>Compare less that  | if (\$2 < \$3) \$1=1; else \$1=0<br>n; 2's comp.         |

| set less than imm.  | slti \$1,\$2,100<br>Compare < consta  | if (\$2 < 100) \$1=1; else \$1=0<br>ant; 2's comp.       |

| set less than uns.  |                                       | if (\$2 < \$3) \$1=1; else \$1=0<br>n; natural numbers   |

| set l. t. imm. uns. |                                       | if (\$2 < 100) \$1=1; else \$1=0<br>ant; natural numbers |

| jump                | j 10000                               | go to 10000                                              |

go to \$31

Lecture 5

31 = PC + 4; go to 10000

31

Jump to target address

For procedure call

For switch, procedure return

jr \$31

jal 10000

jump register

jump and link

UTCS

CS352, S05